|

封裝摩爾定律將取代ICs摩爾定律时间:2019-11-27 【转载】 在過去的六十年,摩爾定律(Moore’s

Law)是晶體管尺寸縮小、晶體管集成和降低成本的驅(qū)動力。但是電子系統(tǒng),比如智能手機、無人駕駛汽車、類人機器人,則不僅僅包含晶體管和ICs。ICs摩爾定律(Moore’s

Law for

ICs)將電子信息產(chǎn)業(yè)引導(dǎo)成長為萬億美元產(chǎn)業(yè),但是ICs摩爾定律(包括約每兩年就增加晶體管集成度、降低成本)由于量子隧穿效應(yīng)等因素,即將到達物理極限。因此,美國佐治亞理工學(xué)院(Georgia

Tech)的Rao R. Tummala教授認為,封裝摩爾定律(Moore’s Law for

Packaging)在短期內(nèi),至少于降低成本方面,將會替代ICs摩爾定律(Moore’s Law for

ICs)。降低晶體管尺寸(即晶體管縮放比例)以及它們的互連和集成度是ICs摩爾定律的基礎(chǔ);而有源、無源系統(tǒng)元件的尺寸減小,及其互連和集成度增加,亦可成為封裝摩爾定律的基石。

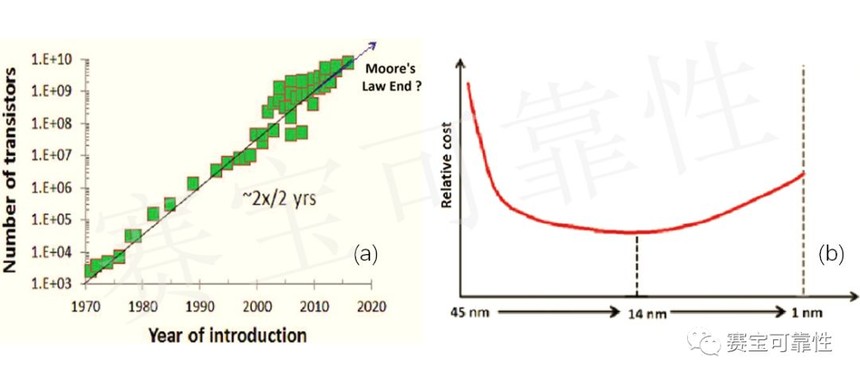

ICs摩爾定律預(yù)測了每18-24個月晶體管數(shù)量增加一倍(圖1a),與此同時成本也隨之降低。因此,Prof. Tummala提出封裝摩爾定律趨勢也類似。其中,互連由計算系統(tǒng)(邏輯和存儲器)驅(qū)動。模擬人腦的人工智能時代的到來,也是封裝摩爾定律的另一驅(qū)動力。

目前,封裝摩爾定律最先進的是基于晶圓的硅封裝(Silicon Packaging)。但是硅基封裝有著諸多限制,如材料、基體、互連及系統(tǒng)。在材料層面,Si基封裝的電損耗和介電常數(shù)很高。在互連層面,Si基封裝的電容和電阻很大,導(dǎo)致RC延遲較大。此外,Si基封裝的在成本層面上與摩爾定律不兼容,而成本對于ICs摩爾定律而言是定律延續(xù)的基礎(chǔ)。在系統(tǒng)層面,與ICs完美兼容的Si中介層(Si-Interposer)與基板(Boards)完全不兼容,需要額外的封裝,因此使得系統(tǒng)級互連長度增加。

圖1 (a)ICs摩爾定律 (b)晶體管柵長與制造成本的關(guān)系

ICs摩爾定律

在過去60年,ICs摩爾定律被事實證明是精準的,且被作為半導(dǎo)體產(chǎn)業(yè)的R&D目標。但是,在晶體管尺寸減小方面,由于量子效應(yīng),當減小至分子級尺寸時,電子隧穿效應(yīng)會導(dǎo)致短路。這是ICs摩爾定律的極限,被稱之為“摩爾定律終結(jié)的開始”(下一個10年內(nèi)即將發(fā)生)。在成本方面,摩爾第二定律指出,在給定尺寸的晶片上,隨著節(jié)點到節(jié)點之間每單位面積晶體管的數(shù)量的增長,每個晶體管的制造成本會下降。而半導(dǎo)體產(chǎn)業(yè)已得出結(jié)論是,當晶體管柵長低于14nm時,單個晶體管的制造成本鮮有降低,反而隨著柵長繼續(xù)減小而有所增長(圖1b)。

封裝摩爾定律:互連密度 or I/Os密度?

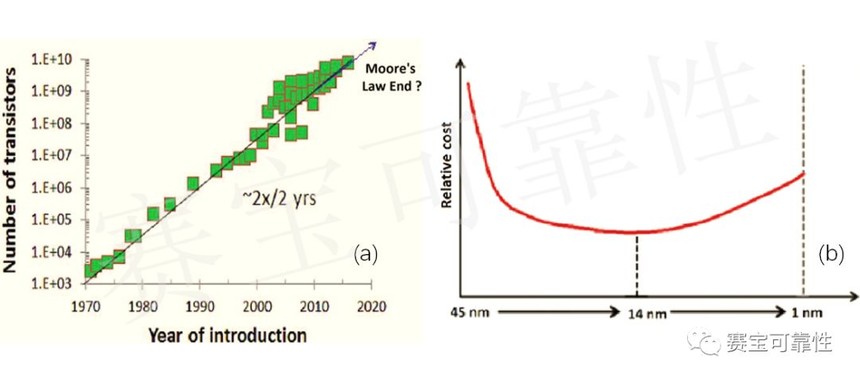

封裝摩爾定律的概念(圖2a)可以從1960年代后期出現(xiàn)的雙列直插式(DIP)封裝形式開始解釋:DIP的I/Os數(shù)<16,隨后出現(xiàn)的外圍四方扁平封裝(QFP)的I/Os數(shù)達到64-304,而后在1980和1990年代,陶瓷封裝的I/Os數(shù)已經(jīng)分別達到了121和1000。但是這個時期的陶瓷封裝有諸多限制,如厚膜粘貼技術(shù)中100μm的線寬和過孔,限制了I/Os數(shù)的繼續(xù)增加。此外,陶瓷的高介電常數(shù)和低電導(dǎo)率(共燒金屬如W,Mo或Ag-Pd)也限制了陶瓷封裝的性能,雖然后期出現(xiàn)的LTCC技術(shù)部分地解決了這些局限性,特別是在頂部制作了類似于重布線層(Redistribution Layer,RDL)的薄膜布線。這些局限性促進了有機層壓封裝的發(fā)展,包括薄膜材料積層及工藝技術(shù),可以使I/Os數(shù)超過5000。當前,大幅提高I/Os數(shù)的唯一辦法是基于晶圓的硅封裝,其I/Os可達到200,000個。

圖2 (a)I/Os封裝摩爾定律(b)封裝類型演進伴隨著單位面積成本降低

封裝摩爾定律:成本

與ICs摩爾定律類似,成本對于封裝摩爾定律也是一個重要因素。圖2b展示了各個封裝類型節(jié)點演進伴隨著單位面積成本的降低趨勢(1980-2020),其中唯一的例外是硅中介層,其成本是封裝摩爾定律預(yù)測值的3-5倍,而佐治亞理工學(xué)院和其工業(yè)合作方共同研發(fā)的玻璃面板封裝(Glass Panel Packaging)的成本是符合封裝摩爾定律預(yù)測趨勢的。

2010年后出現(xiàn)的兩種封裝形式:硅封裝互連(Silicon Package Interconnections)及嵌入式封裝互連(Embedded Package Interconnections)。

硅封裝是最先進的多芯片封裝,I/Os數(shù)可達200,000個,延續(xù)了IBM在1990年代的”100-chip”的多芯片陶瓷封裝的概念,沿用了同樣的功率分配、信號傳輸、芯片背面散熱、倒裝芯片組裝技術(shù)。除此之外,還新開發(fā)了兩個關(guān)鍵技術(shù):硅通孔(TSV)和RDL。博世(Bosch)在高帶寬存儲產(chǎn)品中的TSV制造工藝將TSV與硅中介層的整合度提升到了相當成熟的水平。RDLs是后段制程BEOL(Back End of Line)工藝前身的重組;與有機封裝或陶瓷封裝相比,BEOL的制造設(shè)備是Si中介層能實現(xiàn)高I/Os數(shù)的重要因素。

目前,Intel在EMIB (Embedded Multi-Die Interconnect Bridge)中采用了2μm線寬的Si中介層,而AMD的HBM(High Bandwidth Memory)中的GPU(Graphics Processing Unit)則是采用了1μm線寬,Xilinx在其FPGA(Field Programmable Gate Array)應(yīng)用中的線寬<0.5μm。AMD對外宣稱其Radeon Fury器件的GPU裸片(尺寸596 mm2)的I/Os達到了190,000個,與Xilinx在其Virtex-7 2000T FPGA產(chǎn)品中的I/Os數(shù)處于相同數(shù)量級。

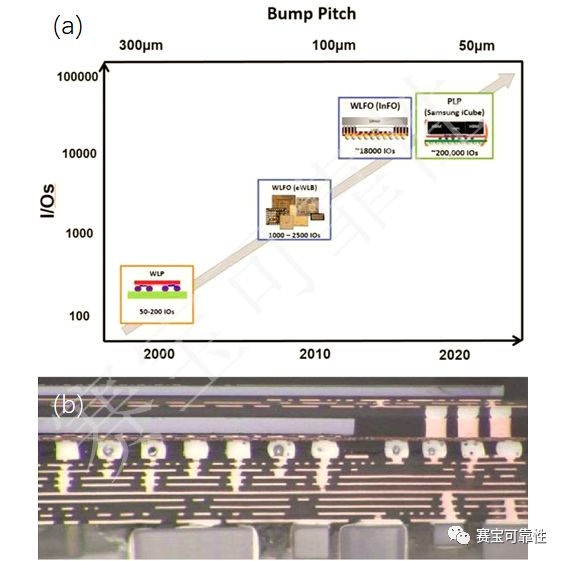

嵌入式封裝意味著芯片是嵌入/埋入到封裝體或板內(nèi),且嵌入的ICs之間的互連則可通過晶圓BEOL工具或封裝工具來實現(xiàn)。圖3a展示了從晶圓級(WLP)、芯片級封裝(CSP)到晶圓級扇出型封裝(WLFO,如eWLB、InFO)、面板級封裝(PLP)技術(shù)的I/Os演變進程。英飛凌(Infineon)是第一家推出面向射頻和模擬應(yīng)用的晶圓扇出封裝(Wafer Fan-Out,WFO)的公司,而臺積電TSMC于2016年為Apple iPhone 7引入了首個大批量嵌入式晶圓扇出封裝(eWFO),即集成型扇出(InFO),見圖3b;當前InFO中約1cm2面積的應(yīng)用處理器中凸點間距(Bump Pitch)為80μm。

圖3 (a)從晶圓級封裝(WLP)到面板級封裝(PLP)的I/Os演化趨勢 (b)臺積電TSMC在iPhone 7中的eWFO封裝

WFO封裝的I/Os數(shù)和終端應(yīng)用場合都在增長,但是也存在著一系列的技術(shù)限制,如裸片放置精度、裸片位置漂移、塑封化合物收縮、晶圓翹曲、大尺寸封裝的板級可靠性、多芯片的可修復(fù)性、散熱、>15mm尺寸封裝的高成本等。面板扇出(Panel-Fanout)技術(shù)的開發(fā)就是為了在有機、無機層壓板的層面上解決上述部分技術(shù)限制,比如佐治亞理工學(xué)院推出的玻璃面板嵌入(Glass Panel Embedding,GPE)技術(shù)及三星的iCube技術(shù)。

封裝摩爾定律的未來

1、擴展Si封裝互連; 2、開發(fā)大面板、低電容和低電阻的無機玻璃面板嵌入式(GPE)封裝; 3、開發(fā)無需塑封化合物和組裝的面板嵌入技術(shù);

4、發(fā)展光電互連技術(shù)。 |